800Gと1.6Tイーサネット:イノベーションと課題

5Gネットワーク、HPCアプリケーション、IoT技術の展開により、より高い帯域幅とデータレートに対する需要が高まっています。その結果、800Gイーサネットと1.6Tネットワーキングへの期待と関心が高まっています。この記事では、800Gイーサネットと1.6Tネットワーキングの主な課題とイノベーションを徹底的に説明します。

イーサネット速度の経時変化

800Gイーサネットと1.6Tネットワークへのアップグレードの課題:

800Gイーサネットの速度と容量を向上させるには?

800Gイーサネットの現在の実装では、1チャネルあたり100Gbpsの8チャネルを使用し、PAM4の速度を50Gbps(前世代)から100Gbpsに倍増させています。チャネルあたり200Gbpsの800Gトランシーバが開発中であり、800Gイーサネットにとって重要な800Gへの挑戦となります。

スイッチ・シリコンSerDes

より高速なネットワーク・スイッチング・チップは、800Gイーサネットのチャネル速度を向上させるために不可欠です。ネットワーク・スイッチング・チップは、データセンター内のエレメント間の低遅延スイッチングを可能にします。スイッチ・チップ全体の帯域幅の増加をサポートするため、SerDesの速度、量、電力も増加しています。51.2Tbps世代では、SerDesの速度は10Gビット/秒から112Gビット/秒に、チップ周辺のSerDesの数は64チャネルから512チャネルに増加した。SerDesの消費電力は、システム全体の電力に占める割合が大きくなっています。102.4Tスイッチには200Gb/秒のSerDesが512チャネル搭載されるため、次世代スイッチング・チップでは帯域幅が再び倍増する。これらのシリコン・スイッチは、224Gb/秒チャネルで800Gと1.6Tをサポートします。

パルス振幅変調

高次変調は、シンボルあたりのビット数または単位インターバル(UI)あたりのビット数を増加させ、チャネル帯域幅と信号振幅のトレードオフを提供します。PAM4変調は、前世代の製品との下位互換性を提供し、高次変調方式と比較して優れた信号対雑音比(SNR)を提供するため、遅延の原因となる前方誤り訂正(FEC)のオーバーヘッドを削減できます。しかし、PAM4を実現するには、アナログ帯域幅の制限と革新的なDSPスキームによって実装される高度なイコライゼーションにより、より優れたアナログ・フロントエンド(AFE)が必要となります。

現在、業界は、高速データ整合性維持のための代替方法を模索しながら、800Gイーサネットまたは1.6TネットワークにおいてPAM4の汎用性を維持する可能性があります。しかし、将来的にはPAM6やPAM8など、より高度な変調方式が採用されるかもしれません。

PAM4信号はアイハイトが小さいため、ノイズとジッターに対してより厳しい設計マージンが必要

800Gイーサネット・ネットワークのビット誤り率を低減するには?

ほとんどの高速データ規格では、トランスミッターとレシーバーに微調整イコライザーが存在することで、チャネル内の信号減衰を補正し、チャネルを通して送信された信号が相手側で解釈できるようになっています。しかし、高速化によって物理的な限界がさらに押し上げられると、より洗練された方法が必要となる。そのようなソリューションのひとつが前方誤り訂正(FEC)です。

フォワード・エラー訂正では、冗長データを送信することで、受信機が損傷したビットの信号を再構築するのを支援します。FECアルゴリズムは、ランダムエラーからデータフレームを回復できるが、フレーム全体が失われるとバーストエラーに遭遇します。各FECアーキテクチャは、符号化利得、オーバーヘッド、レイテンシ、電力効率の点でトレードオフと利点がある。224Gb/秒システムでは、バースト・エラーを最小化するために、より複雑なFECアルゴリズムが必要となります。

異なるFECアーキテクチャにはさまざまなトレードオフがある

|

FECスキーム

|

オプションの例

|

コーディングゲインオーバーKP FEC

|

オーバーヘッド

|

レイテンシ

|

電力/面積

|

|---|---|---|---|---|---|

|

エンドツーエンド

|

RS (576,514,31)

|

-1.5 dB増加

|

6%増加

|

増分増加

|

増分増加

|

|

セグメント化

|

KPとFECo

|

FECo優位

|

FECo優位

|

大幅な増加

|

大幅な増加

|

|

連結

|

KP+BCH/ハミング

|

~0.5-1.5 dB

|

3% -6% 増加

|

増分増加

|

増分増加

|

800Gイーサネットの電力効率を高めるには?

800Gまたは1.6Tイーサネット・データセンターが直面する最も困難な問題は、消費電力である。光モジュールの消費電力は、世代を重ねるごとに増加しています。光モジュールの設計が成熟するにつれて、より効率的になり、その結果、ビットあたりの消費電力が減少します。しかし、各データセンターには平均5万個の光モジュールが搭載されているため、モジュール全体の消費電力は依然として懸念事項となっています。コ・パッケージされた光デバイスは、光電子変換をパッケージ内に統合することで、モジュールあたりの消費電力を削減できます。しかし、このアプローチでは冷却要件が依然として課題となっています。

800Gイーサネットでは、コ・パッケージ型光デバイスの重要なイノベーションは、光コンポーネントをスイッチASICのベアダイに十分に近づけることで、追加のDSPを不要にすることです(下図)。

プラグ可能およびパッケージ化された光学部品

800Gイーサネットと1.6Tネットワーキングのタイムラインは?

800Gイーサネットは、IEEEとOIFが400Gのために築いた基礎の上に構築され、目前に迫っています。最初の51.2Tスイッチチップは2022年にリリースされ、800Gb/秒の64ポートをサポートし、800G光モジュールの初期ロットの検証が開始されました。

今年は、標準化団体がIEEE 802.3dfとOIF 224Gb/s標準の最初のバージョンをリリースし、開発者は112Gb/sと224Gb/sチャネルを使用した800Gと1.6Tシステムの構築方法について理解を深めることができます。今後2年間で、標準化団体は物理層標準を確定し、その後すぐに実際の開発と検証を進めると予想されます。

Timeline for Upgrading to 800G and 1.6T Speeds

FS 800Gイーサネットモジュール

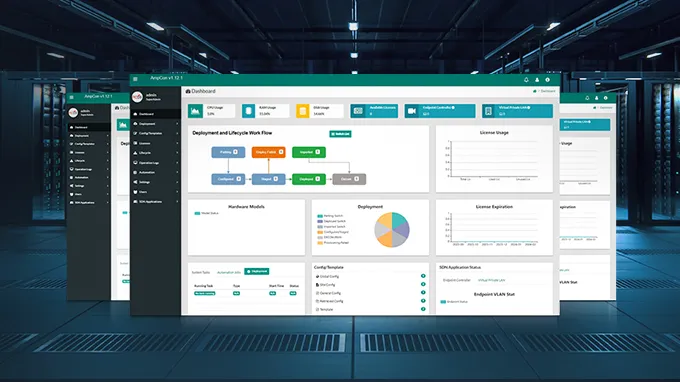

FSは、高性能コンピューティングの現在の発展展望に対応するために、一連の800Gイーサネット モジュールを提供しています。当社の800Gイーサネットモジュールは、現代のネットワークの絶えず変化するニーズを満たすために、信頼性を考慮して設計およびテストされています。以下は、FSの800Gイーサネットモジュールです。

|

FS P/N

|

消費電力 | コネクタ | 距離 |

| QDD-SR8-800G | ≤13W | MTP/MPO-16 | 50m |

| QDD-DR8-800G | ≤16.5W | MTP/MPO-16 | 500m |

| QDD800-PLR8-B1 | ≤18W | MTP/MPO-16 | 10km |

| OSFP-SR8-800G | ≤14W | Dual MTP/MPO-12 | 50m |

| OSFP-DR8-800G | ≤16.5W | Dual MTP/MPO-12 | 500m |

| OSFP-2FR4-800G | ≤16.5W | Dual LC Duplex | 2km |

| OSFP800-PLR8-B1 | ≤16.5W | MTP/MPO-16 | 10km |

| OSFP800-PLR8-B2 | ≤16.5W | Dual MTP/MPO-12 | 10km |

| OSFP800-2LR4-A2 | ≤18W | Dual LC Duplex | 10km |

結論

現在、400Gは大規模に展開されており、800Gイーサネットのデータ・レートにはまだ長い道のりがある。わずか数年のうちに、大容量化、高速化、大幅な効率化が求められるのは間違いない。これらの新技術の拡張に備えるためには、今日から設計と計画を開始する必要があります。FSは、お客様の800Gオプティクスのパートナーになる用意があります。

お勧めの記事

メールアドレス

-

レイヤ2(L2)スイッチとレイヤ3(L3)スイッチ、ルーターとの違いは?

2022年06月20日

-

電源コードの種類・規格について:国内規格と海外規格の選定

2022年06月09日

-

ハブ、スイッチとルーターの違いをわかりやすく解説

2024年08月29日

-

PoEインジェクター(パワーインジェクター)とは?

2022年06月24日

-

T568AとT568B:ストレートケーブルとクロスケーブルの違い

2022年06月30日